- #Diptrace export library for free

- #Diptrace export library manual

- #Diptrace export library full

- #Diptrace export library verification

Some hobby and educational groups such as the PICAXE forum members have developed libraries specific to the PICAXE range of microcontroller as produced by Revolution Education including many of the frequently used associated integrated circuits.

#Diptrace export library manual

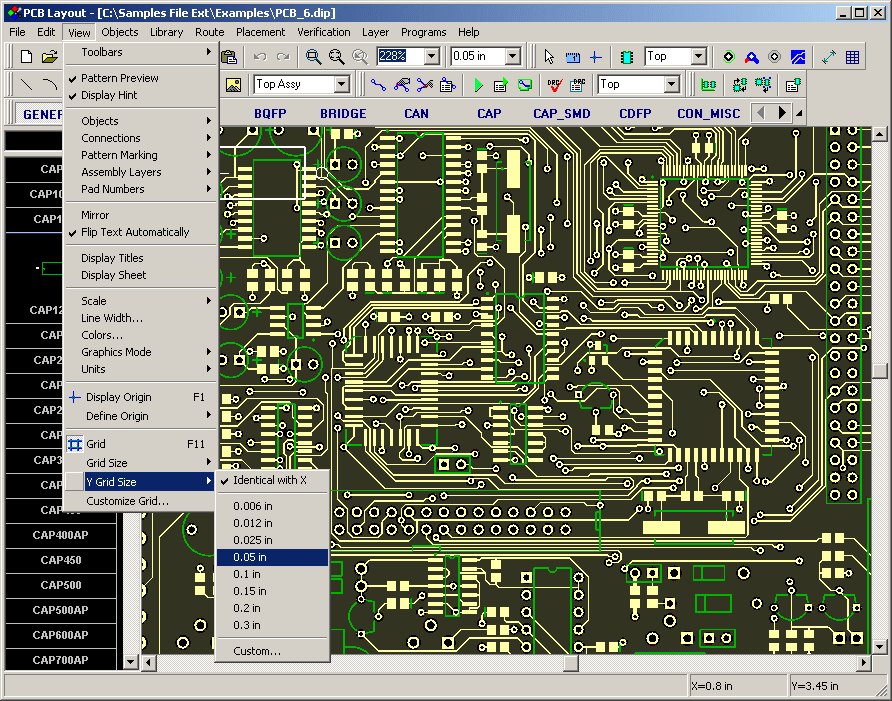

Differential pairs: define differential pair and its rules automatic or manual defining of paired pads paired routing and editing of differential pair single-track differential pair routing and editing phase tune tool (place custom / regular size meanders) real-time control of phase and length tolerance differential pair manager support of differential pairs for external autorouters, recognition of paired traces.

#Diptrace export library full

Power and ground plane layers do not count as signal layers, so the free versions can create four-layer boards with full power and ground planes.

#Diptrace export library for free

‡ Ī version of DipTrace is freely available with all the functionality of the full package except that it is limited to 300 pins and non-commercial use or 500 pins (non-commercial use, contact for free upgrade) and two signal layers.

Manage component libraries and create single- or multi-part components by selecting a template and its dimensions, defining visual and electrical pin parameters, setting up a Spice model, and attaching pattern with a 3D model to finalize component creation.

#Diptrace export library verification

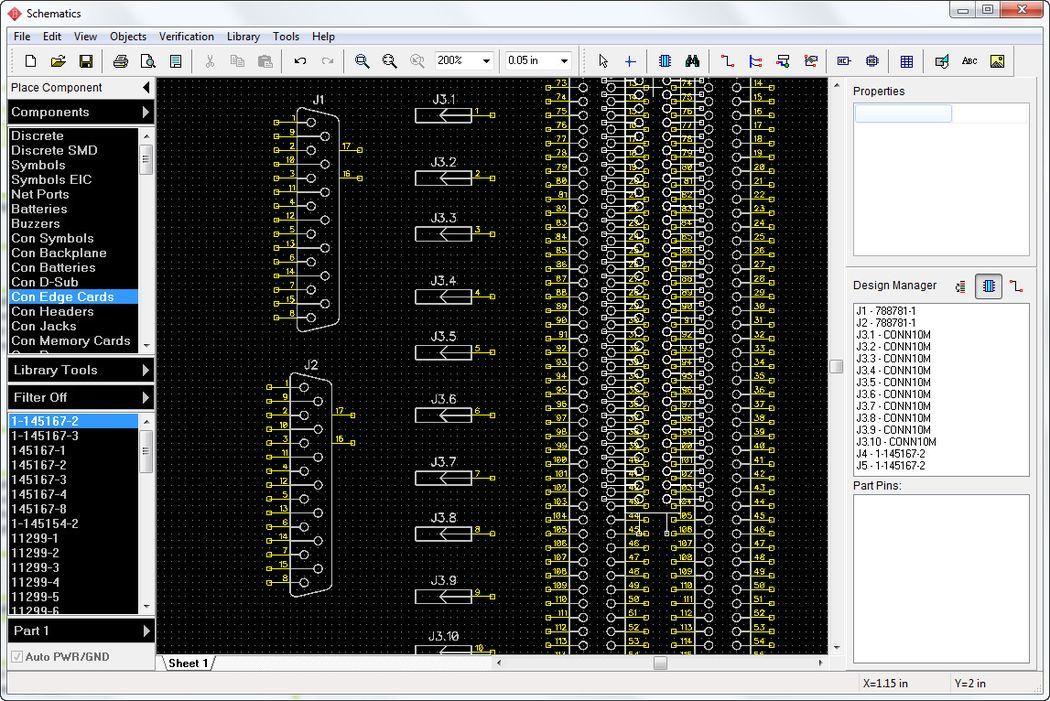

Design rule check with in-depth detailing and net connectivity verification procedures are available. The board can be previewed in 3D and exported to STEP format for mechanical CAD modeling. DRC also checks length and phase tolerances for differential pairs and controls signal synchronization for nets and buses (including layer stackup and bonding wire induced signal delays). When routing with real-time DRC, the program reports errors on the fly before actually making them. Design requirements are defined by net classes, class-to-class rules, and detailed settings by object types for each class or layer. DipTrace Schematic has ERC verification and Spice export for external simulation.Įngineering tool for board design with smart manual routing, differential pairs, length-matching tools, shape-based autorouter, advanced verification, layer stackup manager, and wide import/export capabilities. Cross-module management ensures that principal circuits can be easily converted into a PCB, back-annotated, or imported/exported from/to other EDA software, CAD formats and net-lists. Screenshot of Schematic Capture in DipTrace v3 (2016)Īdvanced circuit design tool with support of multi-sheet and multi-level hierarchical schematics that delivers a number of features for visual and logical pin connections.

0 kommentar(er)

0 kommentar(er)